# Fully Integrated Low Phase-Noise VCOs With On-Chip MEMS Inductors

Eun-Chul Park, Yun-Seok Choi, Jun-Bo Yoon, *Member, IEEE*, Songcheol Hong, *Member, IEEE*, and Euisik Yoon, *Member, IEEE*

**Abstract**—We present fully integrated high-performance voltage-controlled oscillators (VCOs) with on-chip microelectromechanical system (MEMS) inductors for the first time. MEMS inductors have been realized from the unique CMOS-compatible MEMS process that we have developed to provide suspended thick metal structures for high-quality ( $Q$ ) factors. Fully integrated CMOS VCOs have been fabricated by monolithically integrating these MEMS inductors on the top of the CMOS active circuits realized by the TSMC 0.18- $\mu$ m mixed-mode CMOS process. Low phase noise has been achieved as  $-124$  and  $-117$  dBc/Hz at 300-kHz offset from carrier frequencies of 1 and 2.6 GHz, respectively, in the fabricated single-chip VCOs.

**Index Terms**—CMOS compatible, inductor, microelectromechanical system (MEMS), monolithic integration, phase noise, voltage-controlled oscillator (VCO).

## I. INTRODUCTION

THE voltage-controlled oscillator (VCO) is one of the important components in RF communication systems. The carrier frequency of most RF oscillators is adjusted by a phase-locked loop (PLL) to select one of many channels because a given transceiver is assigned different carrier frequencies at different times [1]. VCOs have been widely used to build RF blocks and have been studied for a long time [2]–[5]. Even though a significant amount of research and work had been carried out, the VCO is still a challenging component among RF designers. It is because more stringent requirements are imposed on VCOs as the need for wireless communications is increasing and new applications are coming into the wireless market at higher frequencies. The major issue in recent VCO research is to achieve monolithic integration of low phase-noise VCOs with low-power consumption at given application frequencies. There have been many attempts to integrate high-performance VCOs into a single chip, including inductors made of top-layer metal interconnection lines available from standard silicon processes such as bipolar junction transistors (BJTs) [6], BiCMOS [7], and CMOS [8], [9]. Among these, CMOS VCOs have drawn high attention because they can easily combine RF parts with

baseband blocks that are already available in CMOS technology. Although CMOS technology has been a mainstream process in the digital design community, it has not been considered as an adequate process for RF circuit modules due to its high noise, low operating frequency, and small transconductance. Recently, the demand for system integration in wireless communications has attracted RF designers to build extensive RF circuit blocks using CMOS processes with the help of recent advancement in performance improvement of deep submicrometer CMOS technologies.

In spite of these endeavors, integrated VCOs still have difficulty in emerging into commercial markets. It is because integrated VCOs using standard silicon processes have a hard time with meeting rigorous communication specifications with enough margin due to their relatively poor characteristics of available passive components such as on-chip inductors. Phase noise, one of the major specifications, is directly related with the quality factor ( $Q$ ) of an  $LC$  tank used in VCOs. Generally, the inductors obtained from standard silicon processes cannot provide sufficient  $Q$  factors. (Typical  $Q$  factors from commercially available silicon processes are less than 12 in 1~5-GHz range [10], [11]). Therefore, it is required to devise a new way of providing high- $Q$  on-chip inductors in order to intrinsically improve the performance of VCOs.

In this paper, we report low phase-noise VCOs monolithically integrated with on-chip microelectromechanical system (MEMS) inductors. We have integrated suspended spiral MEMS inductors using surface micromachining technology and have achieved high- $Q$  factors over 25 at 1–4 GHz [12], [13]. These suspended MEMS structures can provide high- $Q$  factors by significantly reducing coupling loss to the substrate. Recently, various MEMS technologies have been applied to fabricate high-performance RF passives, such as switches [14], [15], tunable capacitors [16], [17], inductors [13], [14], transformers [18], [19], and transmission-line and phase shifters [19], [20]. Although all of these RF passives demonstrated high performance, they are standalone off-chip components and have not been integrated with active circuit devices such as a monolithic RF module without a substrate etch [21]. Here, we have successfully integrated MEMS inductors on the top of the CMOS active circuits by employing low-temperature post-CMOS processes. To the best of our knowledge, we are the first to construct a fully integrated VCO with air-suspended MEMS inductors. In this paper, we report design issues, fabrication, and measured performance of the integrated VCO with MEMS inductors in the following sections.

Manuscript received April 24, 2002. This work was supported in part by the Ministry of Science and Technology under the Frontier 21 Program and by the Ministry of Education and Human Resource Development, Korea, under the BK 21 Program.

The authors are with the Division of Electrical Engineering, Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology, Daejeon 305-701, Korea (e-mail: ecpark@iml.kaist.ac.kr).

Digital Object Identifier 10.1109/TMTT.2002.806510

## II. PHASE NOISE

Phase noise is an important performance measure of VCOs and indicates how pure the signal that the VCO generates is in the frequency domain. For an ideal oscillator, the shape of the spectrum is an impulse at a resonant frequency  $\omega_0$ . However, in actual oscillators, skirt shape is formed around  $\omega_0$ . Information recovery from RF signals is seriously affected by this phase noise of VCOs in RF systems [1]. Phase noise can be expressed as signal-to-noise power ratio in unit bandwidth at an offset of  $\Delta\omega$  from an oscillation frequency. A simple equation for the phase noise can be written by [22]

$$PN = 10 \log \left\{ \frac{2FkT}{P_s} \cdot \left[ 1 + \left( \frac{\omega_0}{2Q_L \Delta\omega} \right)^2 \right] \cdot \left( 1 + \frac{\Delta\omega_{1/f^3}}{|\Delta\omega|} \right) \right\} \quad (1)$$

where  $F$  is the empirical parameter,  $k$  is the Boltzmann constant,  $T$  is the absolute temperature,  $P_s$  is the signal power,  $\omega_0$  is the oscillation frequency,  $Q_L$  is the loaded  $Q$  of an  $LC$  tank,  $\Delta\omega$  is the offset frequency, and  $\Delta\omega_{1/f^3}$  is the corner frequency at which the slope of phase noise changes from  $-30$  to  $-20$  dB/dec.

### A. General Considerations

There are two noise sources that contribute phase noise: thermal noise and flicker noise. Phase noise decreases at 20 dB/dec with respect to offset frequency by the effect of thermal noise, while it decreases at 30 dB/dec by flicker noise. Flicker-noise upconversion is related with the symmetry of a signal waveform and can be reduced by designing VCO signal swings symmetrically [4]. It has been reported that the effect of flicker noise in CMOS transistors can be confined to below 100 kHz, although flicker noise itself in CMOS devices exists over 1 MHz. Thermal noise is proportional to the transconductance of active devices. Active devices in the oscillator generate negative conductance to compensate for the loss in a passive  $LC$  tank. If the conductance is too small, it stops VCOs from oscillation. If the conductance is too large, it generates excess thermal noise that may increase phase noise. Therefore, transconductance should be optimized in order to sustain oscillation in a sufficient signal amplitude without introducing excessive noise.

Another important issue is quality factor ( $Q$ ) of the passive elements in an  $LC$  tank of VCOs. It is well known that phase noise decreases inversely proportional to the square of the loaded  $Q$  in an  $LC$  tank, as shown in (1). When inductors are formed by using standard integrated circuit (IC) processes, the quality factor of inductors is a limiting factor and mainly determines the total  $Q$  of an  $LC$  tank. Various circuit schemes and their analysis have been reported to improve phase noise by optimizing circuits [3], [4]. However, the fundamental limit in improving phase noise still remains an issue, unless low-quality factors in the  $LC$  tank itself can be significantly improved.

### B. Transconductance and Phase Noise

Thermal noise becomes a more dominant factor in phase noise than flicker noise in recent RF VCOs. It is because wider

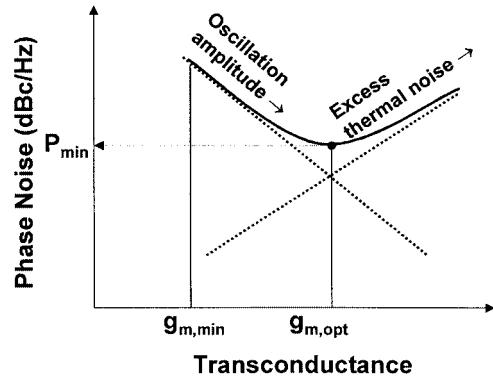

Fig. 1. Transconductance effect on phase noise.

channel bandwidth is required as data transfer rates become higher in new RF communication systems. This implies that phase noise of VCOs at higher offset frequencies becomes more important. Typically, system phase-noise requirement is specified at higher frequencies than the corner frequency of VCOs. Therefore, thermal noise becomes a dominant factor that determines phase noise.

As explained in the previous section, transconductance can be optimized in a given VCO. Fig. 1 shows the transconductance effect on phase noise. The VCO starts oscillating when transconductance reaches to the point  $g_{m,\min}$  and it barely compensates for the dissipation in a passive  $LC$  tank. After this point, phase noise decreases as transconductance increases because oscillation amplitude becomes larger. However, there is a counter effect. Thermal noise in active CMOS devices increases as transconductance and tail current become larger. Therefore, phase noise reaches the minimum at the point that the signal amplitude effect is completely nullified by thermal noise increase. After passing the minimum point, phase noise increases as the signal amplitude is limited to the supply voltage, while thermal noise continuously increases with the increase of transconductance. Therefore, at any given VCO circuit schemes, there exists an optimum transconductance for the minimum phase noise.

### C. Quality-Factor Effects

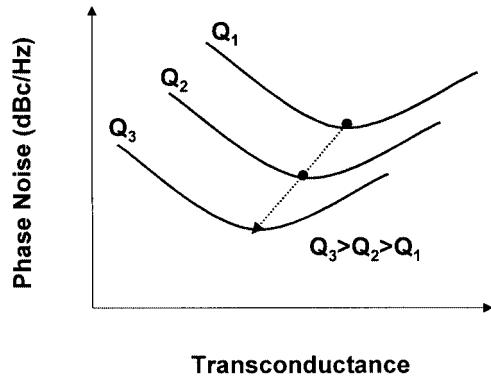

Fundamentally, phase noise is limited by the quality factor of an  $LC$  tank, although the VCO circuit can be designed to give symmetric signal swings and transconductance can be optimized for a given thermal noise. Fig. 2 shows the quality-factor effect on phase noise. Phase noise decreases as  $Q$  increases at a fixed transconductance due to a noise-sharpening effect. As the  $Q$  of an  $LC$  tank increases, the spectrum of the oscillator is sharpened and the noise injected by active devices decreases. Further phase-noise reduction can be achieved by adjustment of transconductance. The optimal transconductances exist at different points with respect to various  $Q$ 's. VCO circuits with higher  $Q$ 's require lower transconductance for the minimum phase noise. Lower transconductance can allow lower power dissipation as well. Therefore, the most effective way to improve phase noise in VCOs is to provide high- $Q$   $LC$  resonators. Higher  $Q$  of the  $LC$  resonator improves phase noise until the  $Q$  of the MOS transistor becomes a limiting factor. Typically, the

Fig. 2. Quality-factor effect on phase noise.

$Q$  of a MOS transistor is higher than that of CMOS inductors [23].

### III. MEMS INDUCTORS

Generally, the inductors obtained from standard silicon processes cannot provide high- $Q$  factors sufficient for high-performance VCOs. The reasons for low- $Q$  factors come from thin metal layers (ohmic loss) and high substrate coupling (eddy-current loss) in standard silicon processes.

Recently, research has been actively carried to find alternative solutions to achieve high- $Q$  inductors from existing silicon processes. Several methods have been proposed to improve  $Q$  factors: bond-wire inductors [24], surface acoustic-wave (SAW) resonators with high  $Q$ 's [25], oxidized porous silicon substrate for thick insulation layer [26], and bulk micromachining for suspended inductor structures [27]. From these methods, high- $Q$  inductors can be achieved, but it is very difficult to monolithically integrate these inductors with on-chip VCO circuits.

We have reported an integrable MEMS fabrication process for RF and microwave MEMS applications [12], [19]. This process allows to fabricate highly suspended metal microstructures that are fully CMOS compatible and manufacturable in terms of process stability and structural robustness. In this section, we will present the RF performance of the suspended spiral inductors fabricated on the standard silicon substrate ( $1\sim30 \Omega \cdot \text{cm}$ ) by using surface micromachining techniques.

#### A. High- $Q$ MEMS Inductors

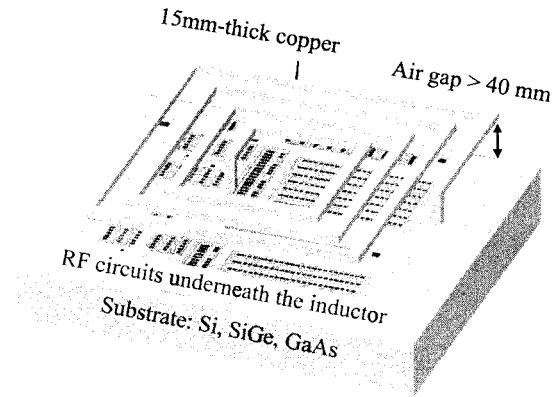

In order to implement high- $Q$  inductors on a silicon substrate, two major loss mechanisms to limit  $Q$ 's in standard CMOS processes have to be minimized. One is ohmic or resistive loss. This loss comes from relatively thin ( $0.5\sim2 \mu\text{m}$ ) metal layers. High resistive loss of these layers plays an important role in determining the  $Q$ 's at a lower frequency region below a  $Q$  peak point. In order to reduce the resistive loss, low-resistivity material should be used as well as the thickness of metal layers should be much larger than skin depth. In this study, we used electroplated thick copper layers, which have a low resistivity of  $1.7 \mu\Omega \cdot \text{cm}$  and the thickness of  $15 \mu\text{m}$ . The  $Q$ 's of inductors start to be saturated at the thickness of  $10 \mu\text{m}$  and there is little increment in  $Q$ 's beyond  $15 \mu\text{m}$ .

The other loss mechanism to be minimized is substrate-induced loss. Integrated passive devices residing on the top of the

Fig. 3. Conceptual schematic of an integrated VCO with on-chip MEMS inductors.

silicon substrate have electromagnetic coupling to the conductive substrate, resulting in substrate loss [28]. In typical CMOS processes with six metal layers, the top layer metal used for inductors is away from the substrate by no less than  $6 \mu\text{m}$  [11] and electromagnetic energy is coupled and dissipated through the lossy substrate. In addition to that, IC foundry recommends RF designers not to put other circuitry beneath and close ( $\sim 50 \mu\text{m}$ ) to CMOS inductors so that the large chip area is consumed by the inductors. This substrate coupling can be significantly reduced by using a suspended metal structure from the substrate. In this study, we built MEMS inductors suspended by  $40 \mu\text{m}$  from the top most layer and could significantly reduce substrate loss.

Fig. 3 shows the conceptual schematic that we have proposed for a single-chip RF transceiver [29]. Active circuit components are fabricated by using standard IC processes and high-performance inductors are monolithically integrated on the top of the circuits by MEMS technology. The features of the proposed MEMS inductors have thick and highly suspended structures for low resistance and low substrate coupling. Due to negligible substrate coupling, MEMS inductors can be stacked on active circuit devices, resulting in the saving of chip area.

#### B. CMOS-Compatible Integration Process

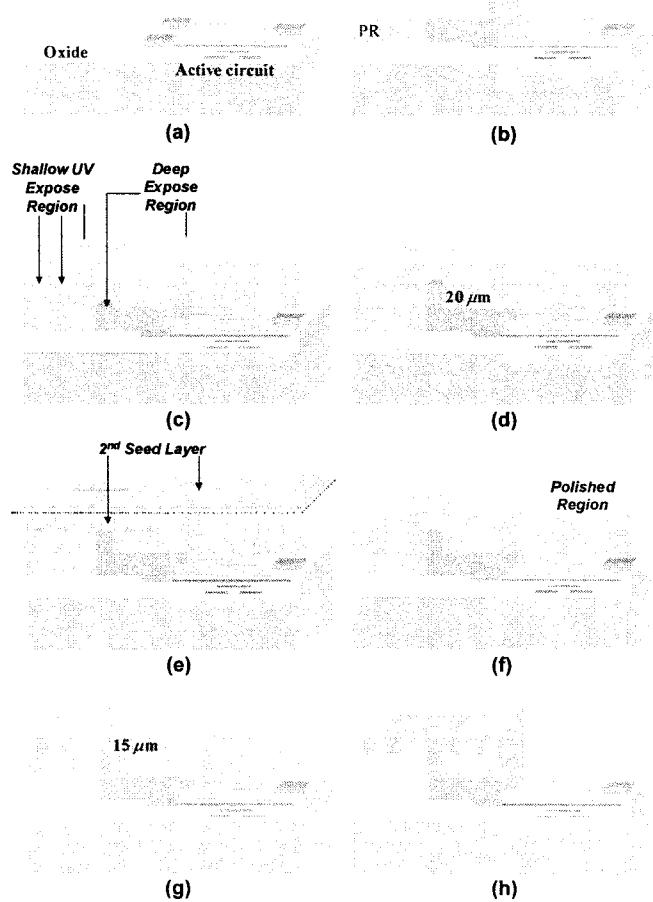

As a post-CMOS process, special surface micromachining processes have been developed to provide a monolithic solution for high- $Q$  inductors by using conventional lithography and electroplating processes. Basically, thick photoresist lithography frequently used in MEMS applications is employed to form an electroplating mold as well as a sacrificial layer. Copper electroplating then follows to fill the patterned photoresist mold. Finally, photoresist is removed.

Detailed process flows are explained in the following [12]. Fabrication starts with a wafer on which CMOS active devices, as well as metal interconnection lines and a top insulation layer with pad openings have been completed [see Fig. 4(a)]. Ti/Cu (20/100 nm) is thermally evaporated as a seed layer for electroplating. Thick photoresist (AZ9260, approximately  $20 \mu\text{m}$ ) is spun and patterned to form electroplating molds. Cu is electroplated through the mold to form bottom electrodes [see Fig. 4(b)]. Second thick photoresist (approximately  $40 \mu\text{m}$ ) is spun on the wafer and the two-step UV exposure

Fig. 4. MEMS inductor integration process.

with two different photomasks and exposure times follows. A three-dimensional (3-D) photoresist mold is formed by single-step development [see Fig. 4(c)]. The thickness of developed photoresist is well controlled by UV expose time [30]. The lower recessed region (approximately  $20\ \mu\text{m}$ ) is filled with the electroplated Cu to form the posts [see Fig. 4(d)]. After the post electroplating, a second seed metal (Cu) is deposited by thermal evaporation on the wafer [see Fig. 4(e)]. The topmost seed metal is removed in order to confine the electroplating of Cu only in the upper recessed region [see Fig. 4(f)]. The dashed line shown in Fig. 4(e) indicates the boundary to which the mechanical polishing is done. Cu is then electroplated from the bottom of upper recessed region [see Fig. 4(g)]. Finally, suspended MEMS structures are completed by removal of photoresist and seed layers [see Fig. 4(h)].

#### IV. DESIGN OF CMOS VCO

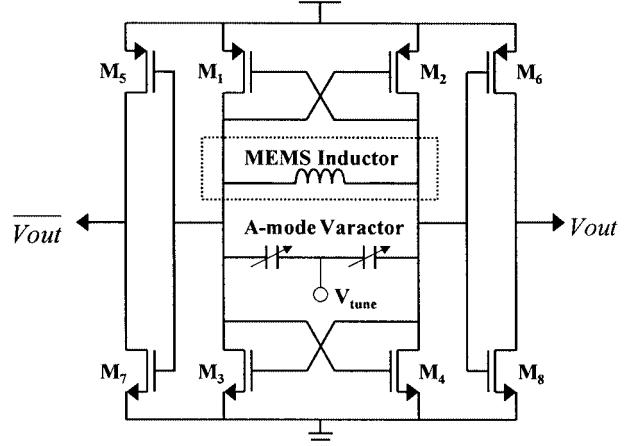

##### A. CMOS Cross-Coupled VCO

In this study, a cross-coupled VCO scheme has been chosen because it can generate large and symmetric signal swings [4]. A circuit schematic of the implemented VCO is shown in Fig. 5. Oscillation frequency is determined by inductance and capacitance in the  $LC$  tank. An accumulation-mode MOSFET varactor known to give a high- $Q$  and a large tuning range has been used for frequency tuning [31]. A MEMS inductor proposed in

Fig. 5. Circuit schematic of CMOS cross-coupled VCO.

the previous section has been implemented for a high- $Q$  resonator. Adequate transconductance of active devices to compensate for the loss in the passive  $LC$  tank is provided by four transistors (M1~M4). To isolate the  $LC$  tank from the  $50\text{-}\Omega$  termination of the spectrum analyzer, four additional transistors (M5~M8) have been used as buffer stages. In this scheme, a current source is not employed in order to maximize signal swings and minimize any noise generated from additional active devices. The output signal is measured via a dc blocking capacitor embedded in the circuit. No additional external components have been used for matching.

##### B. VCO Circuit Optimization

An oscillator is a positive feedback system consisting of an  $LC$  resonator and a loss-compensation amplifier. There are two design guidelines to achieve low phase-noise VCOs: one is to maximize the  $Q$  of an  $LC$  resonator and the other is to minimize the upconversion of noise from the amplifier at a given  $Q$ , as described in Section II. Design procedure begins from the optimization of an  $LC$  resonator. The total  $Q$  of an  $LC$  resonator is typically limited by the  $Q$  of the inductor. In this study, MEMS inductors have been designed to give a maximum  $Q$  at the operating frequencies. We first fixed the width and space of inductors as  $30$  and  $20\ \mu\text{m}$ , respectively. These numbers are determined to achieve a sufficient process margin for inductor fabrication in a reasonable size. The adequate MEMS inductor dimension is then optimized by using 3-D field simulations, which will be confirmed by the measurement of fabricated inductors on a test wafer. The dimensions of the inductors are  $220\ \mu\text{m}$  in the inner diameter with  $3.25$  turns for  $1\text{-GHz}$  operation and  $220\ \mu\text{m}$  in the inner diameter with  $2.25$  turns for  $2.6\text{-GHz}$  operation, respectively. The target inductances are  $5$  and  $1.8\text{ nH}$ , respectively. The corresponding capacitors in the  $LC$  resonators are determined to be  $5$  and  $2\text{ pF}$  for  $1\text{-}$  and  $2.6\text{-GHz}$  operations, respectively.

To minimize the noise conversion effect, the Agilent ADS simulation tool has been used. The active devices optimization procedure has been proceeded in the following two steps.

- Step 1) The ratio of nMOS and pMOS transistors have been optimized for flicker noise reduction.

- Step 2) The actual nMOS transistor widths have been determined for thermal noise reduction.

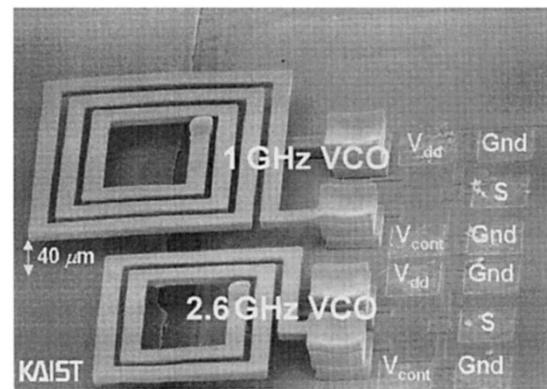

Fig. 6. SEM photograph of fabricated MEMS inductors suspended from the substrate by  $40\ \mu\text{m}$ .

Fig. 7. Measurement pattern to characterize MEMS inductors.

From simulation results, we have obtained the optimal ratio of nMOS and pMOS transistors as 1:2.5, regardless of nMOS size. The result agrees with the inverse ratio of nMOS and pMOS mobilities. This means the optimized VCO will generate a maximum swing of symmetric signals at this ratio. After determining the transistor ratio, the final width of nMOS transistors has been optimized as  $16\ \mu\text{m}$  (with  $4\text{-}\mu\text{m}$ -width legging) for minimal phase noise at the given  $Q$  factor.

## V. EXPERIMENTAL RESULTS

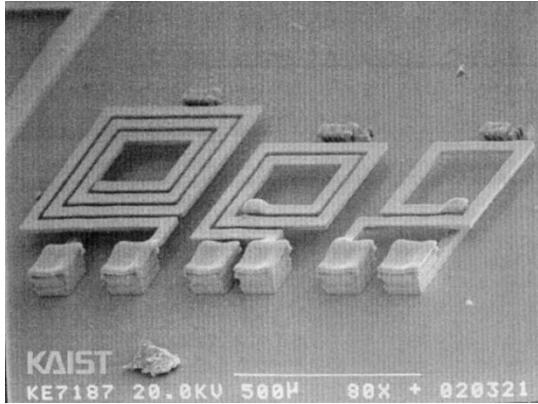

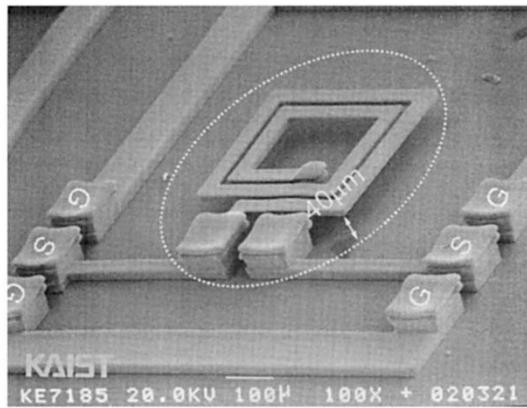

### A. MEMS Inductor Performance

Fig. 6 shows the fabricated MEMS inductors using surface micromachining technology on a silicon test wafer. The test wafer has  $1\text{-}\mu\text{m}$ -thick oxide on the top of the substrate silicon ( $10\ \Omega\cdot\text{cm}$ ) for electrical isolation. The main body of the MEMS inductors is suspended from the substrate by  $40\ \mu\text{m}$ . To characterize the fabricated inductors, on-wafer RF measurement has been performed from 0.1 to 10 GHz using an HP8720 network analyzer. Measurement patterns and deembedding patterns have been fabricated on the same wafer. Fig. 7 shows a measurement pattern of  $1.8\text{-nH}$  MEMS inductors. A pad deembedding process has been conducted to exclude parasitic components of the pads incorporated in measurement patterns.

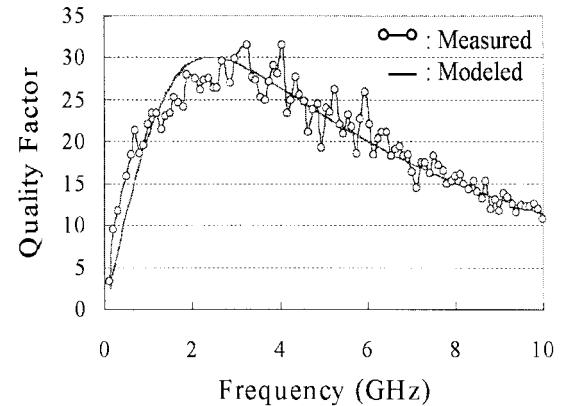

After deembedding, only the intrinsic characteristics of MEMS inductors (inner circle of Fig. 7) can be extracted. The measured and simulated  $Q$ 's of the fabricated MEMS inductor

Fig. 8. Measured quality factor of  $1.8\text{-nH}$  MEMS inductor.

Fig. 9. SEM photograph of fully integrated CMOS VCOs with MEMS inductors.

of  $1.8\text{ nH}$  are shown in Fig. 8. Similar characteristics have been obtained from the measurement of  $5\text{-nH}$  MEMS inductor. The measured  $Q$ 's of MEMS inductors are 20 for  $5\text{-nH}$  inductors at 1 GHz and 27 for  $1.8\text{-nH}$  inductors at 2.6 GHz, respectively. The actual  $Q$ 's of the integrated MEMS inductors are expected to be higher than these measured values because they will be integrated on the top of the CMOS chip, which may have additional insulation layers (with the total thickness of approximately  $6\ \mu\text{m}$ ).

### B. Phase Noise of Integrated VCO

Monolithic VCOs have been fabricated by integrating MEMS inductors on the top of the active circuits realized using the TSMC  $0.18\text{-}\mu\text{m}$  CMOS process. The fabricated VCOs are shown in Fig. 9.

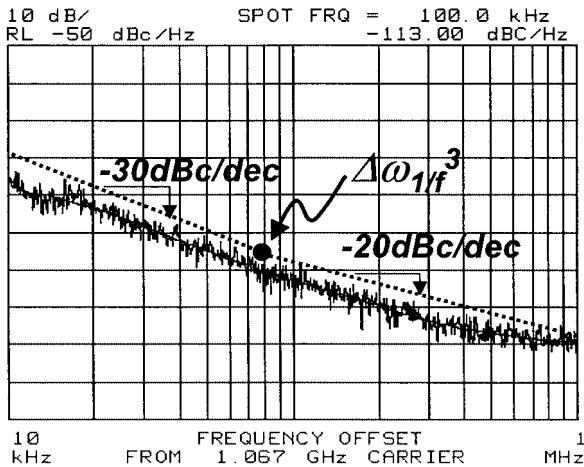

Phase noise has been measured using an HP8564E spectrum analyzer and its characteristics for the 1-GHz oscillator are shown in Fig. 10 as an example. Similar characteristics have been measured for the 2.6-GHz VCO. Low phase noise has been measured as  $-124\text{ dBc/Hz}$  for the 1-GHz VCO and  $-117\text{ dBc/Hz}$  for the 2.6-GHz VCO at 300-kHz offset, respectively.

Detailed measurement results are summarized and compared with recently reported results of CMOS VCOs [32]–[37] in Table I. Although excellent low phase noise has been achieved, the fabricated VCO could not fully utilize the high performance of MEMS inductors. Unfortunately, unlike the assumption

Fig. 10. Measured phase noise of 1-GHz VCO.

TABLE I

MEASURED RESULTS COMPARED WITH OTHER CMOS VCOs

| Ref.                  | Freq.<br>(GHz) | Tuning<br>(MHz) | PN<br>@300kHz<br>(dBc/Hz) | V <sub>DD</sub><br>(V) | I <sub>supply</sub><br>(mA) | FOM<br>[5] |

|-----------------------|----------------|-----------------|---------------------------|------------------------|-----------------------------|------------|

| 1GHz<br>(This work)   | 1              | 750<br>(70%)    | -124                      | 3                      | 5                           | 183        |

| 2.6GHz<br>(This work) | 2.6            | 1600<br>(61%)   | -117                      | 3                      | 5                           | 184        |

| [32]<br>Quad.*        | 1.8            | 330<br>(20%)    | -117                      | 2                      | 25                          | 176        |

| [33]<br>Trans.**      | 1.7            | 107<br>(6.3%)   | -129                      | 2.5                    | 4.5                         | 193        |

| [34]                  | 1.8            | 540<br>(30%)    | -116                      | 2.5                    | 4                           | 182        |

| [35]<br>Quad.*        | 2.45           | 400<br>(15%)    | -105                      | 1.8                    | 3                           | 174        |

| [36]<br>Quad.*        | 2.4            | 300<br>(14%)    | -104                      | 2.5                    | 13                          | 161        |

| [37]                  | 2.5            | 400<br>(17%)    | -110                      | 3                      | 12                          | 174        |

\*Quad: Quadrature VCO, \*\*Trans: Transformer-based VCO

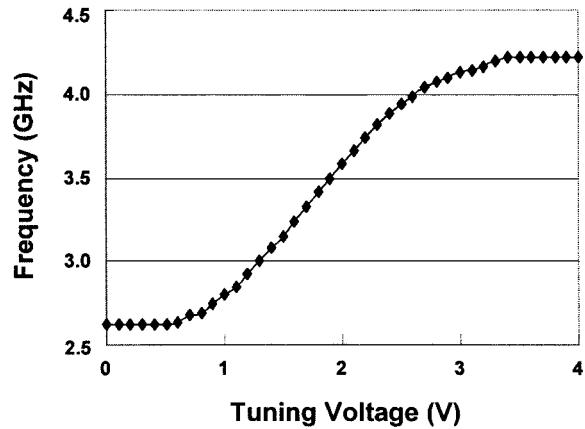

in the design, the actual varactor  $Q$  has been measured as approximately ten at the operating frequencies. There has been some phase-noise degradation compared with simulation. This is because the fabricated varactor has been designed to give an excessive wide tuning range. At least 5-dB improvement can be expected in phase noise, if the varactor  $Q$  were to be 20, as assumed. The  $Q$  of varactors is inversely proportional to its capacitance value at a given frequency. This means a smaller varactor has a higher  $Q$ . Therefore, a higher  $Q$  can be achieved by combining a smaller varactor and a high- $Q$  fixed capacitor in parallel at a cost of reduced the tuning range. From phase-noise data shown in Fig. 10, it can be noted that the corner frequency exists below 100 kHz. This indicates that the fabricated VCO has been fully optimized for reducing flicker noise. The VCO tuning range has been measured by varying the control voltage of the varactor from 0 to 4 V. The oscillation frequency has been tuned from 1.08 to 1.83 GHz and from 2.6 to 4.2 GHz for the 1- and 2.6-GHz VCOs, respectively. Fig. 11 shows the measured tuning characteristics of the 2.6-GHz VCO. VCOs consume 15 mW in the VCO core from a 3-V power supply.

Fig. 11. Tuning characteristics of the 2.6-GHz VCO.

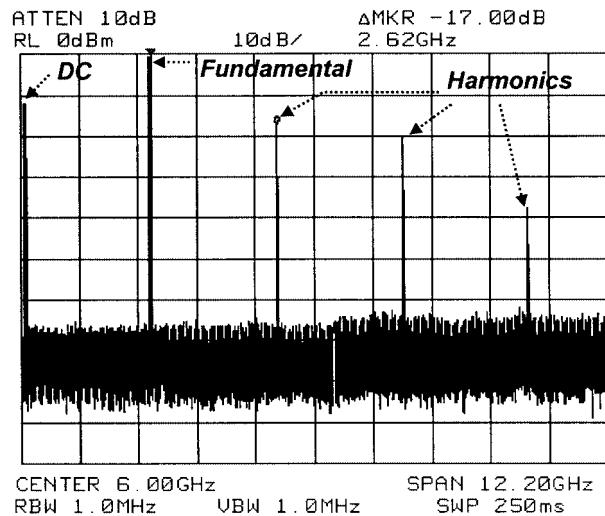

Fig. 12. Output spectrum of the 2.6-GHz VCO.

Fig. 12 shows the output spectrum of the fabricated 2.6-GHz VCO.

## VI. CONCLUSIONS

In order to achieve high-performance fully integrated CMOS VCOs, high- $Q$  MEMS inductors have been monolithically integrated on the top of VCO circuit cores. We have achieved high- $Q$  factors over 20 at 1 GHz and 27 at 2.6 GHz, respectively, in the suspended spiral MEMS inductors fabricated using surface micromachining technology. A differential VCO core circuit has been designed and optimized for low phase noise and has been fabricated by the TSMC 0.18- $\mu$ m CMOS process. From the integrated VCOs with on-chip MEMS inductors, low phase noise has been achieved as  $-124$  dBc/Hz for the 1-GHz VCO and  $-117$  dBc/Hz for the 2.6-GHz VCO at 300-kHz offset from the center frequencies, respectively. We have demonstrated for the first time that the integrated MEMS inductors can give a fully monolithic solution for high-performance on-chip VCOs.

## ACKNOWLEDGMENT

This work was performed as part of the National Research Laboratory Program of the Ministry of Science and Technology.

## REFERENCES

[1] B. Razavi, *RF Microelectronics*. Upper Saddle River, NJ: Prentice-Hall, 1998.

[2] ———, “A study of phase noise in CMOS oscillators,” *IEEE J. Solid-State Circuits*, vol. 31, pp. 331–343, Sept. 1996.

[3] J. Crannicx, M. Steyaert, and H. Miyakawa, “A fully integrated spiral-LC CMOS VCO set with prescaler for GSM and DCS-1800 systems,” in *Custom Integrated Circuits Conf.*, 1997, pp. 403–406.

[4] A. Hajimiri and T. Lee, “A general theory of phase noise in electrical oscillators,” *IEEE J. Solid-State Circuits*, vol. 33, pp. 179–194, Feb. 1998.

[5] F. Herzel, M. Pierschel, P. Weger, and M. Tiebout, “Phase noise in a differential CMOS voltage-controlled oscillator for RF applications,” *IEEE Trans. Circuits Syst.*, vol. 47, pp. 115–131, Mar. 2000.

[6] C. Samori, A. Zanchi, S. Levantino, and A. L. Lacaita, “A fully-integrated low-power low-noise 2.6-GHz bipolar VCO for wireless applications,” *IEEE Microwave Wireless Comp. Lett.*, vol. 11, pp. 199–201, May 2001.

[7] J. Mourant, J. Imbornone, and T. Tewksbury, “A low phase noise monolithic VCO in SiGe BiCMOS,” in *IEEE RFIC Symp.*, 2000, pp. 65–68.

[8] G. Grau *et al.*, “A current-folded up-conversion mixer and VCO with center-tapped inductor in a SiGe-HBT technology for 5-GHz wireless LAN applications,” *IEEE J. Solid-State Circuits*, vol. 35, pp. 1345–1352, Sept. 2000.

[9] M. Harada, T. Tsukahara, and J. Yamada, “0.5–1 V 2 GHz RF front-end circuits in CMOS/SIMOX,” in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, 2000, pp. 378–379.

[10] C.-C. Tang, C.-H. Wu, and S.-I. Liu, “Miniature 3-D inductors in standard CMOS process,” *IEEE J. Solid-State Circuits*, vol. 37, pp. 471–480, Apr. 2002.

[11] *Manual of TSMC 0.18  $\mu$ m Mixed Mode Process*.

[12] J.-B. Yoon, B.-I. Kim, Y.-S. Choi, and E. Yoon, “3-D lithography and metal surface micromachining for RF and microwave MEMS,” in *IEEE Int. Microelectromech. Syst. Conf. Tech. Dig.*, Jan. 2002, pp. 673–676.

[13] J.-B. Yoon, Y.-S. Choi, B.-I. Kim, Y. Eo, and E. Yoon, “CMOS-compatible, surface micromachined, suspended spiral inductors for multi-GHz silicon RF ICs,” *Electron Device Lett.*, vol. 23, pp. 591–593, Oct. 2002.

[14] L. Katehi, J. Harvey, and E. Brown, “MEMS and Si micromachined circuits for high-frequency applications,” *IEEE Trans. Microwave Theory Tech.*, vol. 50, pp. 858–866, Mar. 2002.

[15] G. Rebeiz and J. Muldavin, “RF MEMS switches and switch circuits,” *IEEE Microwave Mag.*, vol. 2, pp. 59–71, Dec. 2001.

[16] J. Park, Y. Yee, H. Nam, and J. Bu, “Micromachined RF MEMS tunable capacitors using piezoelectric actuators,” in *IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 3, May 2001, pp. 2111–2114.

[17] D. Young and B. Boser, “A micromachined-based RF low-noise voltage-controlled oscillator,” in *Custom Integrated Circuit Conf.*, 1997, pp. 431–434.

[18] Y.-S. Choi, J.-B. Yoon, B.-I. Kim, Y. Eo, and E. Yoon, “A high-performance MEMS transformer for silicon RF IC’s,” in *IEEE Int. Microelectromech. Syst. Conf. Tech. Dig.*, Jan. 2002, pp. 653–656.

[19] E.-C. Park, Y.-S. Choi, J.-B. Yoon, S.-C. Hong, and E. Yoon, “Monolithically integrable RF MEMS passives,” *J. Semiconduct. Technol. Sci.*, vol. 2, pp. 49–55, Mar. 2002.

[20] N. Barker and G. Rebeiz, “Optimization of distributed MEMS transmission-line phase shifters—U-band and W-band designs,” *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 1957–1966, Nov. 2000.

[21] J. Chang, A. Abidi, and M. Gaitan, “Large suspended inductors on silicon and their use in a 2- $\mu$ m CMOS RF amplifier,” *IEEE Electron Device Lett.*, vol. 14, pp. 246–248, May 1993.

[22] D. B. Lee, “A simple model of feedback oscillator noises spectrum,” *Proc. IEEE*, vol. 54, pp. 329–330, Feb. 1966.

[23] C.-M. Hung, B. Floyd, N. Park, and K. O, “Fully integrated 5.35-GHz CMOS VCO’s and prescalers,” *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 17–22, Jan. 2001.

[24] T. Ahrens and T. Lee, “A 1.4-GHz 3-mW CMOS LC low phase noise VCO using tapped bond wire inductances,” in *Low Power Electron. and Design Symp.*, 1998, pp. 16–19.

[25] A. Isobe, M. Hikita, K. Asai, and A. Sumioka, “A miniature high-Q grating-mode-type saw resonator and a wide-band 1-GHz saw-VCO for mobile communications,” in *IEEE MTT-S Int. Microwave Symp. Dig.*, 2000, pp. 917–920.

[26] C. M. Nam and Y.-S. Kwon, “High-Performance planar inductor on thick oxidized porous silicon (OPS) substrate,” *IEEE Microwave Guided Wave Lett.*, vol. 7, pp. 236–238, Aug. 1997.

[27] J. Yeh, J. Hongrui, H. Neves, and N. Tien, “Copper-encapsulated silicon micromachined structures,” *J. Microelectromech. Syst.*, vol. 9, pp. 281–287, Sept. 2000.

[28] A. Niknejad and R. Meyer, *Design, Simulation and Applications of Inductors and Transformers for Si RF IC’s*. Boston, MA: Kluwer, 2000.

[29] J.-B. Yoon, “Three-dimensional microstructure technology for microfluidic systems and integrated inductors,” Ph.D. dissertation, Dept. Elect. Eng. Comput. Sci., KAIST, Daejeon, Korea, 1999.

[30] J.-B. Yoon, C.-H. Han, E. Yoon, and C.-K. Kim, “Monolithic fabrication of electroplated solenoid inductors using three-dimensional photolithography of a thick photoresist,” *Jpn. J. Appl. Phys.*, pt. 1, vol. 37, no. 12B, pp. 7081–7085, Dec. 1998.

[31] F. Svelto, S. Deantonio, and R. Castello, “A 1.3 GHz low-phase noise fully tunable CMOS LC VCO,” *IEEE J. Solid-State Circuits*, vol. 35, pp. 356–361, Mar. 2000.

[32] P. Andreani, “A low-phase-noise low-phase-error 1.8 GHz quadrature CMOS VCO,” in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, 2002, pp. 228–229.

[33] M. Straayer *et al.*, “A low-noise transformer-based 1.7 GHz CMOS VCO,” in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, 2002, pp. 286–287.

[34] R. Aparicio and A. Hajimiri, “A CMOS differential noise-shifting Colpitts VCO,” in *IEEE Int. Solid-State Circuits Conf. Tech. Dig.*, 2002, pp. 288–289.

[35] D. Leenaerts *et al.*, “A 0.18  $\mu$ m CMOS 2.45 GHz low-power quadrature VCO with 15% tuning range,” in *IEEE RFIC Symp.*, 2002, pp. 67–70.

[36] B. Chi and B. Shi, “Integrated 2.4 GHz CMOS quadrature VCO with symmetrical spiral inductors and differential varactors,” in *IEEE RFIC Symp.*, 2002, pp. 451–454.

[37] R. Bunch and S. Raman, “A 0.35  $\mu$ m CMOS 2.5 GHz complementary- $G_M$  VCO using PMOS inversion mode varactors,” in *IEEE RFIC Symp.*, 2001, pp. 49–52.

**Eun-Chul Park** was born in Taegu, Korea. He received the B.S. degree in electronic engineering from the Kyungpook National University, Taegu, Korea, in 1996, the M.S. degree in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Taejeon, Korea, in 1998, and is currently working toward the Ph.D. degree at KAIST.

His current interest concerns the integrated MEMS RF module. His current research focuses on high-performance VCOs for RF and microwave applications using MEMS structures.

**Yun-Seok Choi** was born in Busan, Korea. He received the B.S. degree in electronics engineering from the Busan National University, Busan, Korea, in 1997, the M.S. degree in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1999, and is currently working toward the Ph.D. degree at KAIST.

His research interests include modeling of RF passive components and 3-D microstructure fabrication technology.

**Jun-Bo Yoon** (S’92–A’99–M’01) received the B.S. (*summa cum laude*), M.S., and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1993, 1995, and 1999, respectively. His doctoral research concerned the development of the three-dimensional microstructure technology (3D MEMS) for microfluidic systems and integrated inductors.

From 1999 to 2000, he was with The University of Michigan at Ann Arbor, as a Post-Doctoral Research Fellow, where he demonstrated a movable dielectric tunable micromechanical capacitor for RF applications. In 2000, he returned a Research Assistant Professor to the Department of Electrical Engineering, KAIST, where he is currently an Assistant Professor. His research interests include microfabrication and nanofabrication (3-D microstructure and nanostructure) technologies, micro/nanosensors and actuators, optical MEMS, bio MEMS, and RF/microwave MEMS.

Dr. Yoon was the recipient of the Third-Place Award of the Student Paper Competition presented at the IEEE Microwave Theory and Techniques Society (IEEE MTT-S) International Microwave Symposium (IMS) in June 1999.

**Songcheol Hong** (S'87–M'88) was born in Korea, in 1959. He received the B.S. and M.S. degrees in electronics engineering from the Seoul National University, Seoul, Korea, in 1982 and 1984, respectively, and the Ph.D. degrees in electrical engineering and computer science from The University of Michigan at Ann Arbor, in 1989.

He is currently a Professor in the Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea. He has been interested in monolithic microwave ICs and novel quantum devices. His current research interests include solid-state power amplifiers, large-signal models for microwave device, and quantum dot and well application.

Dr. Hong is a member of KITE.

**Euisik Yoon** (S'80–M'82) received the B.S. and M.S. degrees in electronics engineering from the Seoul National University, Seoul, Korea, in 1982 and 1984, respectively, and Ph.D. degree in electrical engineering from The University of Michigan at Ann Arbor, in 1990.

From 1990 to 1994, he was with the Fairchild Research Center, National Semiconductor Corporation, Santa Clara, CA, where he was engaged in research on deep-submicrometer CMOS integration and advanced gate dielectrics. From 1994 to 1996, he was a Member of Technical Staff with Silicon Graphics Inc., Mountain View, CA, where he was involved with the design of the MIPS microprocessor R4300I and the RCP 3-D graphic coprocessor. In 1996, he joined the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, where he is currently an Associate Professor. His current research interests are MEMS, integrated microsystems, and very large scale integration (VLSI) circuit design.

Dr. Yoon has served on various Technical Program Committees including the Microprocesses and Nanotechnology Conference, International Sensor Conference, and IEEE Asia-Pacific Conference on Application Specific Integrated Circuits (ASICs). He currently serves on the IEEE International Solid-State Circuits Conference (ISSCC) Program Committee and Transducers Technical Program Committee.